本发明专利技术提供了一种基于共享内存机制的FPGA硬件抽象层设计方法及系统,配置多个MOCB端口用于软件组件的数据输入/输出,并分配内存空间以获得多个内存空间。一个内存空间指定一个逻辑地址;封装不同的物理总线和IO接口,构建驱动适配接口;建立地址映射表和事件映射表寄存器传输级,实现各个内存空间的起始地址和逻辑地址的映射和软件化事件ID和组件数据发送和接收事件的逻辑地址的对应;建立优先级仲裁表,根据逻辑地址的优先级对事件的发送和接收进行仲裁,并将高优先级逻辑地址对应的事件通过数据路由发送到逻辑地址指定的MOCB端口。本发明的专利技术保证了数据的实时性和可靠性,同时保证了硬件抽象层可以移植到不同的平台上。硬件抽象层可跨不同平台移植。硬件抽象层可跨不同平台移植。硬件抽象层可跨不同平台移植。硬件抽象层可跨不同平台移植。硬件抽象层可跨不同平台移植。硬件抽象层可跨不同平台移植。

下载所有详细的技术数据

【技术实现步骤总结】

基于共享内存机制的FPGA硬件抽象层设计方法及系统

该专利技术涉及电子设备

具体涉及一种基于共享内存机制的FPGA硬件抽象层的设计方法和系统,同时提供了相应的终端和介质。

技术介绍

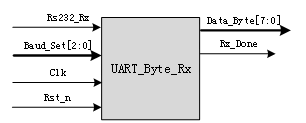

异构嵌入式分布式系统通常包括FPGA、GPP、DSP等异构资源,与同一系统的FPGA资源的处理器类型、外部通信的物理总线(如PCIE、SRIO、EMIF等)存在差异. 为了保证软件组件在不同FPGA上的可移植性,采用MOCB硬件抽象层设计技术,通过引入中间层软件屏蔽底层物理接口的差异。MOCB 是一个接口规范,没有规定硬件抽象层的实现细节。但是现有的MOCB硬件抽象层设计技术无法满足高实时性(延迟、抖动、吞吐量等)和高可靠性的应用需求,这使得复杂的高实时性和高可靠性系统的软件难以组件化,无法在各种平台上使用。间移植。

技术实现思路

[0003] 本专利技术针对现有技术的上述不足,提供了一种基于共享内存机制的FPGA硬件抽象层的设计方法,以及相应的终端和介质。

根据本专利技术的一个方面,提供了一种基于共享内存机制的FPGA硬件抽象层设计方法,包括:

根据应用需要,为软件组件数据输入/输出配置多个MOCB端口,对每个所述MOCB端口进行内存空间分配,得到多个内存空间,每个所述内存空间指定一个逻辑地址;

封装不同的物理总线和IO接口,构建驱动适配接口;

建立所述MOCB端口与所述驱动适配接口之间的数据路由;

建立地址映射表和事件映射表;根据地址映射表,对每个内存空间的起始地址信息进行转换,并将起始地址信息映射到逻辑地址。基于事件映射表对应软件组件的数据收发事件的事件ID的逻辑地址;

构造优先级仲裁表,根据优先级仲裁表中逻辑地址的优先级对软件组件的数据收发事件的发送和接收进行仲裁,将高优先级逻辑地址对应的数据通过所有的数据被路由到逻辑地址指定的MOCB端口,FPGA硬件抽象层的构建完成。

可选地,所述MOCB端口包括:发送缓冲模块、接收缓冲模块、事件复用寄存器模块和流控模块;其中:

所述发送缓存模块,用于暂存所述软件组件要发送的数据,并按照先进先出的原则依次进行数据传输;

所述接收缓存模块,用于暂存需要发送给所述软件组件的数据,按照先进先出的原则,依次向所述软件组件发送数据;

所述的事件复用寄存器模块用于存储多个事件,每个事件对应唯一的事件ID,每个事件ID包括若干子事件;

所述流量控制模块,用于控制所述接收缓冲模块和所述发送缓冲模块的流量,当所述发送缓冲模块和/或所述接收缓冲模块的剩余空间低于设定的阈值时,触发流控信号以停止缓冲模块接收新数据。

[0015] 可选地,驱动适配接口包括:数据通道接口、事件通道接口、射频控制接口和管理通道接口。

可选的,地址映射表实现发送缓冲模块和接收缓冲模块的存储空间的逻辑地址和起始地址的映射,包括索引、逻辑地址和起始地址。起始地址字段;

[0017] 对发送缓冲器模块和接收缓冲器模块的存储器空间分配由软件组件确定。

可选的,所述事件映射表实现所述事件复用寄存器模块与子事件的对应关系,包括:事件ID、逻辑地址、偏移量和字节数n字段;

所述事件复用寄存器模块的每一位对应一个子事件;

所述事件复用寄存器模块的长度为字节的整数倍;

[0021] 事件多路复用寄存器模块的大小由事件映射表中的字节数n指定。

可选的,所述MOCB端口还包括以下任意一个或任意多个模块:

流量统计模块,该模块用于统计所述MOCB端口收发的实时数据流量;

[0024] 数据校验模块,该模块用于校验MOCB端口的数据完整性和正确性。

可选的,软件组件的数据发送和接收包括以下三个过程:

所述软件组件向所述MOCB端口的发送缓冲模块发送数据;

所述MOCB端口将所述发送缓冲模块中的数据发送到物理总线;

[0028] 软件组件从其他软件组件接收数据并且需要通过MOCB端口发送。

可选的,所述软件组件向所述MOCB端口的发送缓冲模块发送数据,包括:

所述软件组件开始发送数据序列,通过所述MOCB端口传输所述发送缓冲模块的存储空间的起始地址信息;

检测所述发送缓冲模块的内存空间大小,当所述发送缓冲模块的内存空间剩余空间大于阈值时,放流控制信号无效;否则,使流量控制信号有效;

所述软件组件向所述发送缓冲模块写入数据包,当发生写入错误时,将所述发送缓冲模块的状态设置为写入异常状态,用于实时写入异常处理;

数据包写入完成后,立即将传输缓冲模块的状态置为空闲状态待发送的数据状态;

[0034] 重复上述步骤,直到软件组件的所有数据传输完成。

可选的,所述MOCB端口将所述发送缓冲模块中的数据发送到物理总线,包括:

等待发送数据请求,所述发送缓冲模块的状态为待发送数据状态,开始向物理总线发送数据的序列;

分析待发送数据的起始地址信息,根据地址映射表分析目标逻辑地址,产生优先级请求信号;

根据优先级请求信号,确定目标逻辑地址对应的优先级,向数据路由发送高优先级目标逻辑地址信息,当发生发送错误时,将发送缓冲模块的状态设置为发送异常状态,用于实时发送异常处理;

所述数据路由根据所述优先级信息和所述目标逻辑地址信息生成路由信息,切换所述物理总线的接口到所述MOCB端口的发送缓冲模块之间的切换;

MOCB口的发送缓冲模块中的数据包由驱动适配接口在物理总线上发送;

发送完一个完整的数据包后,将预设的事件信息发送到目标逻辑地址,并通知数据发送完毕;

[0042] 重复上述步骤,当传输缓存模块中所有待发送数据的传输完成后,设置传输缓存模块的状态为空闲状态。

可选的,所述软件组件接收来自其他软件组件的数据,需要通过所述MOCB端口发送,包括:

[0018] 所述软件组件在接收到数据到达事件信号时,分析对应逻辑地址和MOCB端口的接收缓冲模块的起始地址信息,并启动响应事件序列;

检测所述MOCB端口的接收缓存模块中是否包含至少一个完整的数据包,如果没有,则

【技术保护点】

【技术特点总结】

1.一种基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,包括:根据应用需要,配置多个用于软件组件数据输入/输出的MOCB端口,每个所述MOCB端口完成了。分配内存空间以获得多个内存空间,其中每个内存空间指定一个逻辑地址;封装不同的物理总线和IO接口,构建驱动适配接口;建立MOCB端口与驱动适配接口之间的数据路由;建立地址映射表和事件映射表;根据地址映射表,对每个存储空间的起始地址信息进行转换,并将起始地址信息映射到逻辑地址。根据事件映射表,将软件组件的数据收发事件的事件ID与逻辑地址对应起来;构造优先级仲裁表,并根据优先级仲裁表中逻辑地址的优先级为软件分配组件的数据收发事件,将高优先级逻辑地址对应的数据通过数据路由发送到逻辑地址指定的MOCB端口,从而完成FPGA硬件抽象层的构建。2.根据权利要求1所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述MOCB端口包括:发送缓冲模块、接收缓冲模块、事件多路复用寄存器模块和流控制模块;其中: 发送缓存模块用于暂存软件组件要发送的数据,并按照先进先出的原则依次发送数据。接收缓冲模块用于暂存需要的数据 发送给软件组件的数据按照先进先出的原则依次发送给软件组件;事件复用寄存器模块用于存储多个事件,每个事件对应一个唯一的事件ID,每个事件ID包括若干子事件。流量控制模块用于控制接收缓冲模块和发送缓冲模块的流量,当发送缓冲模块和/或接收缓冲模块的区域模块剩余空间低于设定阈值时,触发流控信号,停止缓冲模块接收新数据;和/或驱动适配接口包括:数据通道接口、事件通道接口、射频控制接口和管理通道接口。

3.根据权利要求2所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述地址映射表实现所述逻辑地址与所述发送缓冲模块和所述接收缓冲模块。内存空间起始地址之间的映射包括索引、逻辑地址和起始地址字段;发送缓冲模块和接收缓冲模块的内存空间分配由软件组件确定。4.根据权利要求2所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述事件映射表实现所述事件复用寄存器模块与子事件的对应关系寄存器传输级,包括:事件ID、逻辑地址、偏移量和字节数 n 个字段;事件复用寄存器模块的每一位对应一个子事件;事件复用寄存器模块的长度为字节乘以整数;事件多路复用寄存器模块的大小由事件映射表中的字节数n指定。5.根据权利要求2所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述MOCB端口还包括以下任意一个或任意多个模块:

流量统计模块,用于统计MOCB端口收发的实时数据流量;数据校验模块,用于校验MOCB端口的数据完整性和正确性。6.根据权利要求2

――

6.根据5任一项所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述软件组件的数据收发包括以下三个过程: 软件组件向MOCB端口发送数据,发送缓冲模块;MOCB端口将发送缓冲模块中的数据发送到物理总线;软件组件从其他软件组件接收数据,需要通过MOCB端口发送。7.根据权利要求6所述的基于共享内存机制的FPGA硬件抽象层设计方法,其特征在于,所述软件组件向所述MOCB端口的发送缓冲模块发送数据,包括:所述软件组件启动发送数据时序,通过MOCB端口传输发送缓冲模块的内存空间的起始地址信息;检测发送缓冲模块的内存空间大小,当发送缓冲模块的内存空间剩余空间大于设定的阈值时,将流控信号设置为无效;否则,流量控制信号设为有效;软件组件将数据包写入发送缓冲模块,当发生写入错误时...

【专利技术性质】

技术研发人员:常坤、吴尔龙、高新春、

申请人(专利权)持有人:上海解放信息技术有限公司,

类型:发明

国家省市:

下载所有详细的技术数据 我是该专利的所有者